理解谷歌在量子纠错方面的突破

对谷歌最新量子纠错论文以及用于容错量子计算的实时解码的未来进行控制者视角的解读。

想象一下,试图同时平衡数千个旋转的陀螺——每个陀螺代表一个量子比特,量子计算机的基本构建块。现在想象一下,这些陀螺非常敏感,即使是微风、轻微的振动或快速一瞥看看它们是否还在旋转,都可能使它们摇晃或掉落。这就是量子计算的挑战:量子比特非常脆弱,即使是控制或测量它们的过程也会引入错误。

这就是量子纠错(QEC)的用武之地。通过将多个脆弱的物理量子比特组合成一个更强大的逻辑量子比特,QEC 使我们能够比错误累积得更快地纠正错误。目标是在低于临界阈值的情况下运行——即增加更多量子比特会减少而不是增加错误的点。这正是 Google Quantum AI 近期突破所实现的 [1]。

谷歌的突破性成就

要理解谷歌成果的意义,首先让我们了解一下纠错的成功是什么样的。在经典计算机中,抗错误的内存是通过复制比特来检测和纠正错误来实现的。一种称为多数投票的方法经常被使用,其中比较一个比特的多个副本,并将多数值作为正确的比特。在量子系统中,物理量子比特被组合起来创建逻辑量子比特,其中通过监测量子比特之间的相关性而不是直接观察量子比特本身来纠正错误。它涉及像多数投票这样的冗余,但不依赖于观察而是纠缠。这种间接方法至关重要,因为直接测量量子比特的状态会破坏其量子特性。有效的量子纠错可以保持逻辑量子比特的完整性,即使某些物理量子比特出现错误,这对于可扩展的量子计算至关重要。

然而,这只有在物理错误率低于临界阈值时才有效。事实上,直觉认为,增加构成逻辑量子比特的物理量子比特的数量应该可以实现更好的纠错。事实上,如果每个物理量子比特都非常容易出错,那么增加量子比特会使错误累积得比我们检测和纠正它们的速度更快。换句话说,只有在任何纠错之前,每个量子比特都可以在低于错误阈值的情况下运行,量子纠错才有效。拥有更多的物理量子比特可以增加 QEC 代码距离,这是衡量量子代码检测和纠正错误的能力的指标。

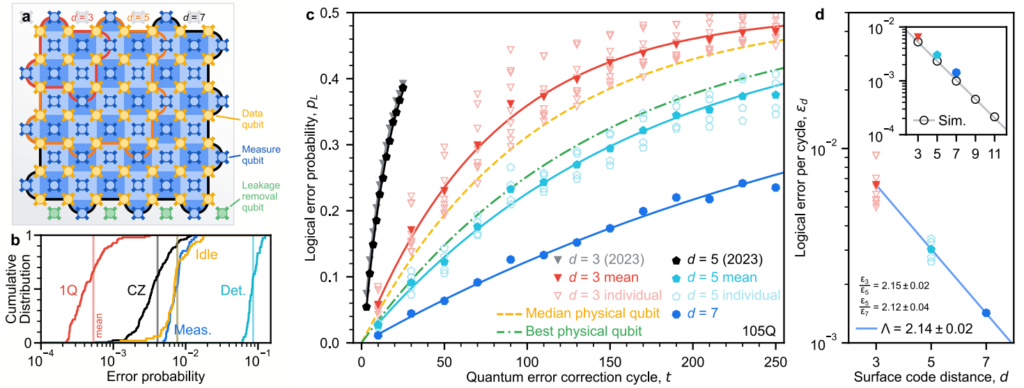

通过展示当代码距离从 5 增加到 7 时,逻辑错误减少了 2.14 倍,谷歌现在已经证明了使用表面代码(一种特定类型的量子纠错代码)的低于阈值运行。这种误差的减少(随着代码距离的增加呈指数级增长)是证明其 QEC 策略有效的确凿证据。有了这一点,谷歌可以证明他们的逻辑量子比特的寿命是他们最好的物理量子比特的两倍以上,如图 1 所示,这表明逻辑量子比特不仅存活下来,而且性能优于物理量子比特。

图 1 – 一个经过调整的图表,显示逻辑量子比特错误率与代码距离的关系,突出了随着代码距离的增加,逻辑错误的指数级抑制。该图说明了过渡到低于阈值性能以及使用距离为 7 的代码实现的“超越盈亏平衡”行为。(改编自 Google Quantum AI 的 [1\],CC BY 4.0)

101 个量子比特上的距离为 7 的表面代码有效地使逻辑量子比特的寿命(图 1c 中的蓝线)与未经校正的物理量子比特(图 1c 中的绿线)相比增加了一倍。这一成就表明,经过纠错的量子比特可以更长时间地保持相干性,这对于运行扩展的量子算法和计算至关重要。

控制工程视角:谷歌如何实现它

该实验不仅仅是对表面代码的测试,它还是一个精心策划的工程和控制壮举。控制系统必须在多个方面提供完美的精度——同步、频率控制、测量保真度、实时解码和稳定性——经过数小时的运行。让我们停下来谈谈其中一些有趣的挑战。

系统的核心是实时同步。每个校正周期都必须在 1.1 微秒内完成——这是一个测量量子比特的狭窄窗口。这种同步的精度对于防止错误累积和破坏计算的稳定性至关重要。实现这一点需要在量子比特阵列中精确协调控制信号,确保每个门操作、测量都完美对齐。

最重要的组件之一是实时解码。解码是指分析测量数据以确定错误发生的位置和方式的过程。为了使用逻辑量子比特执行通用量子计算,必须应用某些称为非克利福德门的门。应用这些门需要在实时解码的基础上实时纠正错误。在谷歌的系统中,实时解码器在运行超过一百万个校正周期时保持大约 63 微秒的恒定延迟。也就是说,实时纠错管道可以足够快地处理测量结果,以避免拥塞。这种快速解码过程至关重要,因为任何延迟都可能导致错误传播和累积,从而可能破坏逻辑量子比特的稳定性。

该实验还需要高保真门操作。量子比特门中的错误很容易在系统中传播,从而危及逻辑量子比特的稳定性。谷歌实现了低于 0.1% 的单量子比特门错误和大约 0.3% 的双量子比特 CZ 门错误——这些阈值对于保持逻辑量子比特随时间推移的稳定至关重要。为此,控制电子设备的高性能至关重要,因为保真度可能会直接因控制脉冲的错误而受损。当扩展表面代码时,这些保真度尤其重要,即使是微小的门错误也可能会降低纠错的有效性。

随着量子计算机扩展到更多量子比特和更长的计算,这些和更多的控制要求只会变得更加苛刻,这使得先进控制硬件的开发对于容错量子计算的未来至关重要。

在上述要求中,特别是实时解码是任何可扩展量子计算系统的基础,因为它提供了保持量子信息稳定所需的快速响应。

深入了解实时解码

谷歌的工作强调,解码的可行性取决于解码器的延迟和吞吐量,这是在阈值以下运行 QEC 的最重要的部分之一。

解码是一项经典的计算任务,可以在各种经典架构上有效地完成,例如 FPGA 或 GPU。然而,计算资源之间通常会存在权衡。例如,FPGA 的计算能力有限,但以确定性方式运行并具有严格的定时,使其适合管理量子比特控制和测量任务以及执行低延迟的专用经典计算。另一方面,CPU 或 GPU 可能会增加延迟,但可以进行更高级和更大的计算。在 Quantum Machines,我们与 NVIDIA 合作 提供了一个独特的平台,称为 DGX Quantum,它提供了超低控制器-解码器延迟、高性能计算能力和灵活的软件可编程性的独特组合。我们的平台(包括我们的控制器 OPX1000 和 CPU/GPU 之间小于 4 微秒的通信)允许轻松编程和执行 QEC 工作流程,包括实时解码,例如谷歌的解码。软件可编程性允许非常快速地迭代解码算法和方案。我们认为这是一个更快地实现可扩展和有效 QEC 的关键功能。事实是,需要进行更多的实验和基准测试,以了解使用哪些解码器、哪些经典资源优化性能并满足要求,以及如何设计最终可以在更大规模上运行 QEC 的系统。我们目前所知的是,对于 QEC 方案收敛,解码器的延迟应小于 10 微秒。观看我们的首席执行官 Itamar Sivan 进一步解释这一点,并以用于分解数字 21 的 Shor 算法为例。

DGX-quantum 已经上线,展示了控制器和 GPU 之间小于 4 微秒的往返延迟。要了解更多信息,请观看以下 IEEE QCE 2024 教程,该教程由 QM 和 NVIDIA 共同撰写,内容涉及 DGX-quantum。

视频教程:将 GPU 和 QPU 紧密集成在一起,用于量子纠错和最优控制。

那么,接下来是什么?

谷歌对低于阈值的量子纠错的演示标志着容错量子计算的一个里程碑。通过证明逻辑量子比特可以优于物理量子比特,并表明错误可以比它们累积得更快地纠正,他们为可扩展的量子处理器铺平了道路。

然而,这仅仅是个开始。未来,要使用经过纠错的逻辑量子比特执行通用量子计算,必须关闭完整的反馈回路,这意味着控制系统需要根据解码器计算实时做出决策。未来的发展将需要更快的解码器、更好的错误缓解策略、嵌入在量子程序中的自动校准以稳定参数,以及紧密集成和管理经典和量子工作流程的控制硬件。

谷歌的成就标志着朝着容错量子计算迈出了重要一步。通过证明逻辑错误率可以通过使用表面代码呈指数级抑制,这项工作为可靠的量子计算提供了一条可扩展且实用的途径。随着代码距离的增加,错误会快速减少,为能够以更高保真度处理复杂操作的量子处理器奠定了基础。此外,这种快速解码的实现代表了 QEC 的一项根本进步。这项技术允许比错误传播更快地纠正错误,从而最大限度地减少错误在量子系统中传播的机会。

量子纠错和容错愿景

实时、低延迟的反馈回路将成为未来容错量子设备的重要组成部分,以确保错误比它们累积得更快地得到纠正。这一原则在更广泛的量子计算社区中引起共鸣,在那里,快速而强大的控制机制被视为实现大规模、可靠量子操作的关键。

正如谷歌的里程碑式成就所表明的那样,通过专注于低延迟、高保真度的反馈和解码,更广泛的量子技术领域正在朝着容错量子计算的共同目标迈进。支持敏捷纠错和实时适应性的量子控制系统的发展将继续在追求稳定、可扩展的量子计算系统中发挥核心作用,这些系统可以部署在实际应用中。借助 DGX-quantum,我们才刚刚开始这段激动人心的旅程,敬请期待未来的发展!

由 NVIDIA 和 Quantum Machines 共同开发的 DGX Quantum 解决方案支持大规模量子计算机的量子纠错、校准和快速重新调整。它允许使用强大的经典资源(GPU 和 CPU)进行量子计算机操作,具有低于 4 微秒的超快数据往返延迟。

参考

[1] Acharya, Rajeev, et al. “量子纠错低于表面代码阈值。” arXiv preprint arXiv:2408.13687 (2024).